-

×

UNIT Kit ESP32 Básico con 10 practicas

1 × $ 269.00

UNIT Kit ESP32 Básico con 10 practicas

1 × $ 269.00 -

×

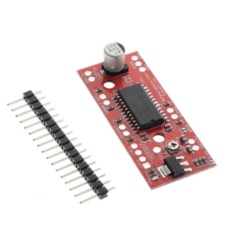

Easydriver Para Motor De Pasos V4.4 Controlador A3967

1 × $ 65.00

Easydriver Para Motor De Pasos V4.4 Controlador A3967

1 × $ 65.00 -

×

Cargador de Carga Rápida 40W US + Cable Tipo C

1 × $ 147.00

Cargador de Carga Rápida 40W US + Cable Tipo C

1 × $ 147.00 -

×

Sonoff SNZB-06P Sensor de Presencia Humana Zigbee

1 × $ 257.00

Sonoff SNZB-06P Sensor de Presencia Humana Zigbee

1 × $ 257.00 -

×

Filamento PLA SILK Negro Seda 1.75mm IIIDMAX

1 × $ 407.00

Filamento PLA SILK Negro Seda 1.75mm IIIDMAX

1 × $ 407.00 -

×

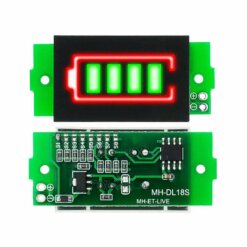

Indicador de Bateria Litio Ajustable 1S a 8S Color Verde

1 × $ 37.00

Indicador de Bateria Litio Ajustable 1S a 8S Color Verde

1 × $ 37.00 -

×

Par de Led IR Infrarrojos Receptor Transmisor 3mm

1 × $ 4.00

Par de Led IR Infrarrojos Receptor Transmisor 3mm

1 × $ 4.00 -

×

Llavero Tag RFID 13.56 MHz NFC

1 × $ 7.00

Llavero Tag RFID 13.56 MHz NFC

1 × $ 7.00 -

×

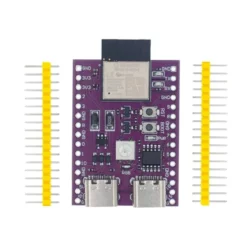

ESP32 C3 Tarjeta de Desarrollo Dual Tipo C

1 × $ 125.00

ESP32 C3 Tarjeta de Desarrollo Dual Tipo C

1 × $ 125.00 -

×

S-160 Tapete Magnético Antiestática 45x30cm

1 × $ 181.00

S-160 Tapete Magnético Antiestática 45x30cm

1 × $ 181.00 -

×

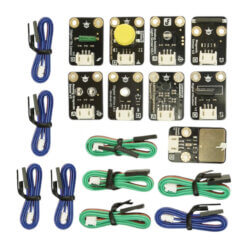

Gravity Kit de 9 Sensores Compatibles con Arduino DFR0018

1 × $ 601.00

Gravity Kit de 9 Sensores Compatibles con Arduino DFR0018

1 × $ 601.00 -

×

Modulo WiFi ESP8266 ESP-12F

1 × $ 53.00

Modulo WiFi ESP8266 ESP-12F

1 × $ 53.00 -

×

Adaptador Micro USB a USB C

1 × $ 20.00

Adaptador Micro USB a USB C

1 × $ 20.00 -

×

MAX232IDR IC SMD Transceptor

1 × $ 23.00

MAX232IDR IC SMD Transceptor

1 × $ 23.00 -

×

Kit Terminal Preaislado tubular VE 2120 Piezas

1 × $ 189.00

Kit Terminal Preaislado tubular VE 2120 Piezas

1 × $ 189.00 -

×

Raspberry Pi Zero 2 W

1 × $ 437.00

Raspberry Pi Zero 2 W

1 × $ 437.00 -

×

RM99BPro Pinza Amperimétrica Digital

1 × $ 336.00

RM99BPro Pinza Amperimétrica Digital

1 × $ 336.00 -

×

1N4004 Diodo Rectificador 1A 400V

1 × $ 1.00

1N4004 Diodo Rectificador 1A 400V

1 × $ 1.00 -

×

TB6600 Driver Para Motor A Pasos 4A Nema

1 × $ 131.00

TB6600 Driver Para Motor A Pasos 4A Nema

1 × $ 131.00 -

×

UNIT DualMCU ONE ESP32 + RP2040

2 × $ 269.00

UNIT DualMCU ONE ESP32 + RP2040

2 × $ 269.00 -

×

Cepillo de Alambre de Latón y Acero Inoxidable para Limpieza de Boquillas

1 × $ 39.00

Cepillo de Alambre de Latón y Acero Inoxidable para Limpieza de Boquillas

1 × $ 39.00 -

×

74LS04 Compuerta NOT SN74LS04N

1 × $ 7.00

74LS04 Compuerta NOT SN74LS04N

1 × $ 7.00

Puede que estés interesado en…

-

Add

Puntas para Multímetro de 1000V 10A

$ 29.00

Puntas para Multímetro de 1000V 10A

$ 29.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Bolsa de Sellado al Vacío para Filamentos

$ 129.00 - $ 137.00Rango de precios: desde $ 129.00 hasta $ 137.00

Bolsa de Sellado al Vacío para Filamentos

$ 129.00 - $ 137.00Rango de precios: desde $ 129.00 hasta $ 137.00 -

Add

MUL-281 Multímetro Profesional RMS con Detector de Voltaje

$ 299.00

MUL-281 Multímetro Profesional RMS con Detector de Voltaje

$ 299.00 -

Add

Kit Agujas de 0.15-0.35mm para Limpieza de Boquillas

$ 72.00

Kit Agujas de 0.15-0.35mm para Limpieza de Boquillas

$ 72.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Conector Neumático Rápido

$ 14.00 - $ 15.00Rango de precios: desde $ 14.00 hasta $ 15.00

Conector Neumático Rápido

$ 14.00 - $ 15.00Rango de precios: desde $ 14.00 hasta $ 15.00

Subtotal: $ 3,874.00

Valoraciones

No hay valoraciones aún.