-

×

Kit Transistores BJT TO-92 200 Piezas 10 Valores

1 × $ 82.00

Kit Transistores BJT TO-92 200 Piezas 10 Valores

1 × $ 82.00 -

×

46205 Clavija Industrial Plástica Aterrizada Volteck

1 × $ 20.00

46205 Clavija Industrial Plástica Aterrizada Volteck

1 × $ 20.00 -

×

Batería LiPo 3.7V 1600mAh 803455

1 × $ 97.00

Batería LiPo 3.7V 1600mAh 803455

1 × $ 97.00 -

×

Kit Hotend para Serie P1 Bambu Lab con Boquilla de Acero Endurecido 0.4mm

1 × $ 499.00

Kit Hotend para Serie P1 Bambu Lab con Boquilla de Acero Endurecido 0.4mm

1 × $ 499.00 -

×

Pluma Flux 951 Kester 10ml Non Clean

1 × $ 59.00

Pluma Flux 951 Kester 10ml Non Clean

1 × $ 59.00 -

×

Maletin de Soldadura con Cautín Regulable 60W

1 × $ 329.00

Maletin de Soldadura con Cautín Regulable 60W

1 × $ 329.00 -

×

S-160 Tapete Magnético Antiestática 45x30cm

1 × $ 181.00

S-160 Tapete Magnético Antiestática 45x30cm

1 × $ 181.00 -

×

Kit Brazo Robótico 6DOF con Garra y Servos

1 × $ 1,040.00

Kit Brazo Robótico 6DOF con Garra y Servos

1 × $ 1,040.00 -

×

Kit de Terminales Preaislado 280pcs FDD, MDD, RV y SV

1 × $ 108.00

Kit de Terminales Preaislado 280pcs FDD, MDD, RV y SV

1 × $ 108.00 -

×

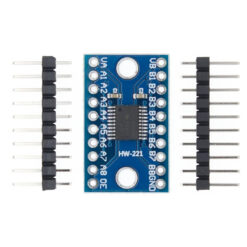

TXS0108E Conversor Lógico 8CH 3.3V a 5V Bidireccional

1 × $ 22.00

TXS0108E Conversor Lógico 8CH 3.3V a 5V Bidireccional

1 × $ 22.00 -

×

7 Botellas de Soldadura de Estaño y Plomo BGA para Reballing

1 × $ 229.00

7 Botellas de Soldadura de Estaño y Plomo BGA para Reballing

1 × $ 229.00 -

×

DP-366D Desoldador de Succión

1 × $ 49.00

DP-366D Desoldador de Succión

1 × $ 49.00 -

×

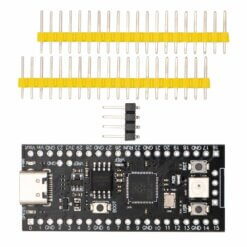

Raspberry Pi RP2040 4 MB USB Tipo C

1 × $ 74.00

Raspberry Pi RP2040 4 MB USB Tipo C

1 × $ 74.00 -

×

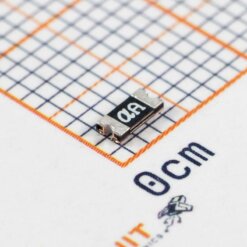

NSMD025-30V Fusible Reseteable 30V 500mA SMD 1206

1 × $ 5.00

NSMD025-30V Fusible Reseteable 30V 500mA SMD 1206

1 × $ 5.00 -

×

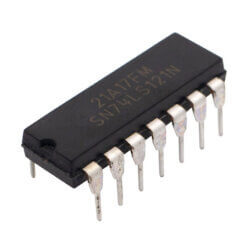

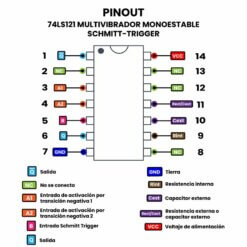

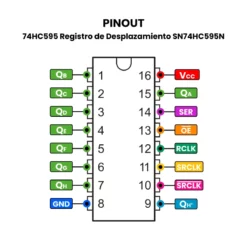

74HC595 Registro de Desplazamiento SN74HC595N

1 × $ 7.00

74HC595 Registro de Desplazamiento SN74HC595N

1 × $ 7.00

Puede que estés interesado en…

-

Add

Pasta Limpiadora para Puntas de Cautín 6g

$ 34.00

Pasta Limpiadora para Puntas de Cautín 6g

$ 34.00 -

Add

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

$ 159.00

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

$ 159.00 -

Add

HB-019 Desoldador de Succión Eléctrico 36W 110V

$ 139.00

HB-019 Desoldador de Succión Eléctrico 36W 110V

$ 139.00 -

Add

Boquilla de Acero Endurecido 0.4mm para P1/X1 Bambu Lab

$ 52.00

Boquilla de Acero Endurecido 0.4mm para P1/X1 Bambu Lab

$ 52.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Bolsa de Sellado al Vacío para Filamentos

$ 129.00 - $ 137.00Rango de precios: desde $ 129.00 hasta $ 137.00

Bolsa de Sellado al Vacío para Filamentos

$ 129.00 - $ 137.00Rango de precios: desde $ 129.00 hasta $ 137.00

Subtotal: $ 2,801.00

Valoraciones

No hay valoraciones aún.