-

×

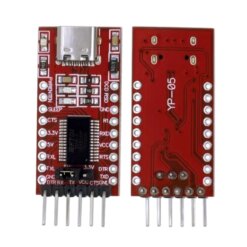

Convertidor USB 6 en 1 TTL CP2102

1 × $ 87.00

Convertidor USB 6 en 1 TTL CP2102

1 × $ 87.00 -

×

46204 Clavija Industrial Plástica Volteck

2 × $ 17.00

46204 Clavija Industrial Plástica Volteck

2 × $ 17.00 -

×

Speaker Altavoz 8 Ohm 1W 20mm

1 × $ 16.00

Speaker Altavoz 8 Ohm 1W 20mm

1 × $ 16.00 -

×

Pelacables Autoajustable con Cortadora de Cable y Crimpado de Terminales

2 × $ 184.00

Pelacables Autoajustable con Cortadora de Cable y Crimpado de Terminales

2 × $ 184.00 -

×

Tira Header Macho 40 Pines 2mm Negro

1 × $ 4.00

Tira Header Macho 40 Pines 2mm Negro

1 × $ 4.00 -

×

XLG-200-12-A Fuente de Alimentación 12V 16A IP67 MEAN WELL

1 × $ 809.00

XLG-200-12-A Fuente de Alimentación 12V 16A IP67 MEAN WELL

1 × $ 809.00 -

×

Congelante Detector de Falla para Circuitos Electrónicos 170 ml SILIJET E-3

1 × $ 109.00

Congelante Detector de Falla para Circuitos Electrónicos 170 ml SILIJET E-3

1 × $ 109.00 -

×

IP2312 Módulo de Carga Rápida 3A 1S

1 × $ 27.00

IP2312 Módulo de Carga Rápida 3A 1S

1 × $ 27.00 -

×

Base Socket 8 Pines IC DIP-8 Slim

1 × $ 2.00

Base Socket 8 Pines IC DIP-8 Slim

1 × $ 2.00 -

×

Amplificador de Audio TPA3116 30W Doble Canal

1 × $ 60.95

Amplificador de Audio TPA3116 30W Doble Canal

1 × $ 60.95 -

×

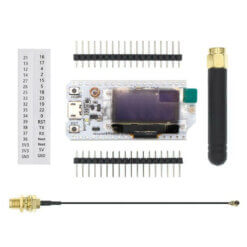

SX1276 ESP32 LoRa 915 MHz OLED 0.96"

1 × $ 395.00

SX1276 ESP32 LoRa 915 MHz OLED 0.96"

1 × $ 395.00 -

×

Zocalo ZIF 40 pines

1 × $ 24.00

Zocalo ZIF 40 pines

1 × $ 24.00 -

×

Soldador de Gas Tipo Bolígrafo con Accesorios

1 × $ 290.00

Soldador de Gas Tipo Bolígrafo con Accesorios

1 × $ 290.00 -

×

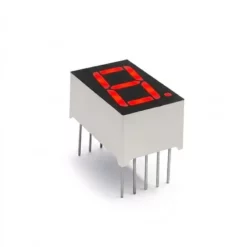

74LS48 Decodificador Display 7 Segmentos SN74LS48N

1 × $ 12.00

74LS48 Decodificador Display 7 Segmentos SN74LS48N

1 × $ 12.00 -

×

1N5399 Diodo Rectificador 1000V 1.5A

1 × $ 2.00

1N5399 Diodo Rectificador 1000V 1.5A

1 × $ 2.00 -

×

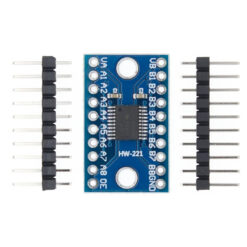

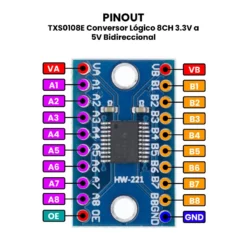

TXS0108E Conversor Lógico 8CH 3.3V a 5V Bidireccional

1 × $ 22.00

TXS0108E Conversor Lógico 8CH 3.3V a 5V Bidireccional

1 × $ 22.00

Puede que estés interesado en…

-

Add

Toallitas Húmedas para Limpieza de Equipos Electrónicos 30pcs COMPUTOALLAS

$ 59.00

Toallitas Húmedas para Limpieza de Equipos Electrónicos 30pcs COMPUTOALLAS

$ 59.00 -

Add

Limpiador Dieléctrico para Circuitos y Tarjetas Electrónicas 454 ml COMPUKLIN

$ 189.00

Limpiador Dieléctrico para Circuitos y Tarjetas Electrónicas 454 ml COMPUKLIN

$ 189.00 -

Add

Limpiador Electrónico en Aerosol 454 ml SILIJET E-7 Plus

$ 169.00

Limpiador Electrónico en Aerosol 454 ml SILIJET E-7 Plus

$ 169.00 -

Add

Espuma Limpiadora para Equipos Electrónicos 454 ml SILIMPO

$ 99.00

Espuma Limpiadora para Equipos Electrónicos 454 ml SILIMPO

$ 99.00 -

Add

Limpiador y Lubricante para Equipos Electrónicos en Aerosol 170 ml SILIJET E-PLUS

$ 89.00

Limpiador y Lubricante para Equipos Electrónicos en Aerosol 170 ml SILIJET E-PLUS

$ 89.00

Subtotal: $ 2,261.95

Valoraciones

No hay valoraciones aún.