-

×

DP-366D Desoldador de Succión

1 × $ 49.00

DP-366D Desoldador de Succión

1 × $ 49.00 -

×

Pasta Limpiadora para Puntas de Cautín 6g

1 × $ 34.00

Pasta Limpiadora para Puntas de Cautín 6g

1 × $ 34.00 -

×

MC7805CD2TR4G Regulador de Voltaje 5V 1A SMD

1 × $ 14.00

MC7805CD2TR4G Regulador de Voltaje 5V 1A SMD

1 × $ 14.00 -

×

Sensor de Humedad con Buzzer Alarma de Riego

1 × $ 89.00

Sensor de Humedad con Buzzer Alarma de Riego

1 × $ 89.00 -

×

Eliminador 9V 1A con Plug

1 × $ 55.00

Eliminador 9V 1A con Plug

1 × $ 55.00 -

×

Kit Micrófono Inalámbrico FM 70-110Mhz

1 × $ 73.00

Kit Micrófono Inalámbrico FM 70-110Mhz

1 × $ 73.00 -

×

28BYJ-48 Motor a Pasos con Controlador ULN2003

1 × $ 52.00

28BYJ-48 Motor a Pasos con Controlador ULN2003

1 × $ 52.00 -

×

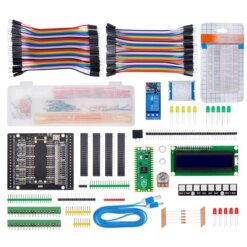

UNIT Pi Pico Kit de Iniciación para Raspberry Pi Pico 27 Practicas

1 × $ 299.00

UNIT Pi Pico Kit de Iniciación para Raspberry Pi Pico 27 Practicas

1 × $ 299.00 -

×

Alcohol Isopropílico en Aerosol 400 ml

1 × $ 79.00

Alcohol Isopropílico en Aerosol 400 ml

1 × $ 79.00 -

×

K215 Controlador de Huellas + R503 Sensor Dactilar

1 × $ 802.00

K215 Controlador de Huellas + R503 Sensor Dactilar

1 × $ 802.00 -

×

Conector de Audio XLR 3 Pines Plateado Hembra y Macho

1 × $ 47.00

Conector de Audio XLR 3 Pines Plateado Hembra y Macho

1 × $ 47.00 -

×

Cautín de 90W 110V con Puntas Soporte y Esponja

1 × $ 283.00

Cautín de 90W 110V con Puntas Soporte y Esponja

1 × $ 283.00 -

×

Plug DC 5.5mm x 2.1mm Barril

1 × $ 6.00

Plug DC 5.5mm x 2.1mm Barril

1 × $ 6.00 -

×

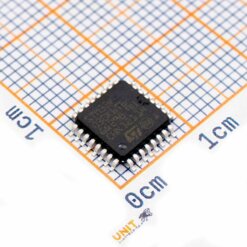

STM32F030K6T6 MCU Arm Cortex-M0 48MHz LQFP-32

1 × $ 38.00

STM32F030K6T6 MCU Arm Cortex-M0 48MHz LQFP-32

1 × $ 38.00 -

×

Sonoff MINIR4M Switch WiFi

1 × $ 236.00

Sonoff MINIR4M Switch WiFi

1 × $ 236.00 -

×

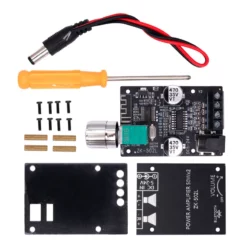

502L Amplificador Bluetooth Estereo 50W

1 × $ 150.00

502L Amplificador Bluetooth Estereo 50W

1 × $ 150.00

Puede que estés interesado en…

-

Add

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

$ 159.00

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

$ 159.00 -

Add

HB-019 Desoldador de Succión Eléctrico 36W 110V

$ 139.00

HB-019 Desoldador de Succión Eléctrico 36W 110V

$ 139.00 -

Add

Limpiador y Lubricante para Equipos Electrónicos en Aerosol 170 ml SILIJET E-PLUS

$ 89.00

Limpiador y Lubricante para Equipos Electrónicos en Aerosol 170 ml SILIJET E-PLUS

$ 89.00 -

Add

Cepillo de Alambre de Latón y Acero Inoxidable para Limpieza de Boquillas

$ 39.00

Cepillo de Alambre de Latón y Acero Inoxidable para Limpieza de Boquillas

$ 39.00 -

Add

UNIT Pulsar ESP32-C6

$ 189.00

UNIT Pulsar ESP32-C6

$ 189.00

Subtotal: $ 2,306.00

Valoraciones

No hay valoraciones aún.