-

×

UNIT Placa de Expansión para Raspberry Pi Pico

1 × $ 79.00

UNIT Placa de Expansión para Raspberry Pi Pico

1 × $ 79.00 -

×

Push Button 2 Pines MicroSwitch

2 × $ 1.00

Push Button 2 Pines MicroSwitch

2 × $ 1.00 -

×

Conector Estéreo de 3.5mm 90 grados Niquelado Negro

1 × $ 16.00

Conector Estéreo de 3.5mm 90 grados Niquelado Negro

1 × $ 16.00 -

×

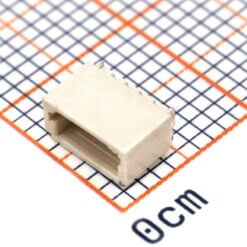

Conector JST SR 4 Pines Horizontal SM04B-SRSS-TB(LF)(SN)

1 × $ 2.10

Conector JST SR 4 Pines Horizontal SM04B-SRSS-TB(LF)(SN)

1 × $ 2.10 -

×

Tornillo Milimétrico M3 x 6 mm con Tuerca M3

1 × $ 3.00

Tornillo Milimétrico M3 x 6 mm con Tuerca M3

1 × $ 3.00 -

×

Sonoff RF Bridge R2

1 × $ 203.00

Sonoff RF Bridge R2

1 × $ 203.00 -

×

Receptor Infrarrojo VS1838B IR Fototransistor

1 × $ 6.00

Receptor Infrarrojo VS1838B IR Fototransistor

1 × $ 6.00 -

×

Eliminador 5V 2A con Plug

1 × $ 68.00

Eliminador 5V 2A con Plug

1 × $ 68.00 -

×

Banda Dentada GT2 2GT 6mm 10 Metros

1 × $ 211.00

Banda Dentada GT2 2GT 6mm 10 Metros

1 × $ 211.00 -

×

Sensor de Humedad Suelo Capacitivo Anticorrosivo

1 × $ 22.00

Sensor de Humedad Suelo Capacitivo Anticorrosivo

1 × $ 22.00 -

×

Alcohol Isopropílico en Aerosol 400 ml

1 × $ 79.00

Alcohol Isopropílico en Aerosol 400 ml

1 × $ 79.00 -

×

TEMT600 Sensor de Luz Ambiental – UNIT DevLab

1 × $ 39.00

TEMT600 Sensor de Luz Ambiental – UNIT DevLab

1 × $ 39.00 -

×

Espuma Limpiadora para Equipos Electrónicos 454 ml SILIMPO

1 × $ 99.00

Espuma Limpiadora para Equipos Electrónicos 454 ml SILIMPO

1 × $ 99.00 -

×

Carcasa de Acrílico Orange Pi Zero2

1 × $ 61.00

Carcasa de Acrílico Orange Pi Zero2

1 × $ 61.00 -

×

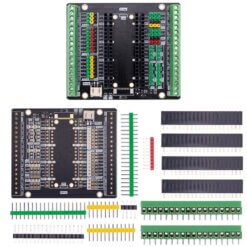

UShieldX Shield de Expansión para Arduino UNO

1 × $ 456.00

UShieldX Shield de Expansión para Arduino UNO

1 × $ 456.00 -

×

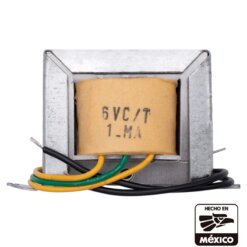

Transformador 6VC/T 1A con Tap Central

1 × $ 153.00

Transformador 6VC/T 1A con Tap Central

1 × $ 153.00 -

×

UNIT Kit Mega 2560 con 31 Practicas

1 × $ 849.00

UNIT Kit Mega 2560 con 31 Practicas

1 × $ 849.00

Puede que estés interesado en…

-

Add

Toallitas Húmedas para Limpieza de Equipos Electrónicos 30pcs COMPUTOALLAS

$ 59.00

Toallitas Húmedas para Limpieza de Equipos Electrónicos 30pcs COMPUTOALLAS

$ 59.00 -

Add

Limpiador Dieléctrico para Circuitos y Tarjetas Electrónicas 454 ml COMPUKLIN

$ 189.00

Limpiador Dieléctrico para Circuitos y Tarjetas Electrónicas 454 ml COMPUKLIN

$ 189.00 -

Add

Limpiador Electrónico en Aerosol 454 ml SILIJET E-7 Plus

$ 169.00

Limpiador Electrónico en Aerosol 454 ml SILIJET E-7 Plus

$ 169.00 -

Add

Congelante Detector de Falla para Circuitos Electrónicos 170 ml SILIJET E-3

$ 109.00

Congelante Detector de Falla para Circuitos Electrónicos 170 ml SILIJET E-3

$ 109.00 -

Add

Limpiador y Lubricante para Equipos Electrónicos en Aerosol 170 ml SILIJET E-PLUS

$ 89.00

Limpiador y Lubricante para Equipos Electrónicos en Aerosol 170 ml SILIJET E-PLUS

$ 89.00

Subtotal: $ 2,348.10

Valoraciones

No hay valoraciones aún.