-

×

Kit de 12 Practicas para Huskylens y Micro:bit KIT0179-EN

1 × $ 1,275.00

Kit de 12 Practicas para Huskylens y Micro:bit KIT0179-EN

1 × $ 1,275.00 -

×

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

1 × $ 159.00

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

1 × $ 159.00 -

×

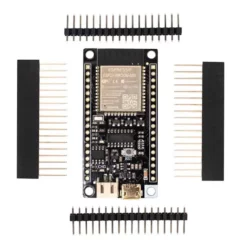

FireBeetle ESP32 IoT WiFi + Bluetooth DFR0478

1 × $ 222.00

FireBeetle ESP32 IoT WiFi + Bluetooth DFR0478

1 × $ 222.00 -

×

TTP223B Sensor Capacitivo Touch - UNIT DevLab

1 × $ 29.00

TTP223B Sensor Capacitivo Touch - UNIT DevLab

1 × $ 29.00 -

×

Sensor de Humedad con Buzzer Alarma de Riego

1 × $ 89.00

Sensor de Humedad con Buzzer Alarma de Riego

1 × $ 89.00 -

×

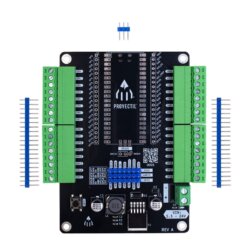

PShieldX Shield de Expansión para Raspberry Pi Pico

1 × $ 456.00

PShieldX Shield de Expansión para Raspberry Pi Pico

1 × $ 456.00 -

×

Sonoff MINIR4M Switch WiFi

1 × $ 236.00

Sonoff MINIR4M Switch WiFi

1 × $ 236.00 -

×

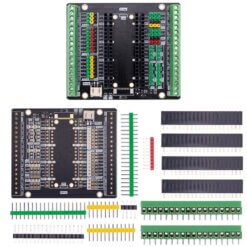

UNIT Placa de Expansión para Raspberry Pi Pico

1 × $ 79.00

UNIT Placa de Expansión para Raspberry Pi Pico

1 × $ 79.00 -

×

Kit Pinza de Compresión para Cable Coaxial RG59/RG6 con Pelador Giratorio + 20 Conectores

1 × $ 179.00

Kit Pinza de Compresión para Cable Coaxial RG59/RG6 con Pelador Giratorio + 20 Conectores

1 × $ 179.00

Puede que estés interesado en…

-

Add

CAU-118 Punta Conica para Cautin CAU-105 y CAU-115

$ 16.00

CAU-118 Punta Conica para Cautin CAU-105 y CAU-115

$ 16.00 -

Add

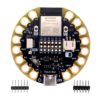

UNIT Touchdot ESP32-S3 WiFi BT

$ 179.00

UNIT Touchdot ESP32-S3 WiFi BT

$ 179.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

GX-9877 Interruptor Tactil Unicolor/Bicolor para Espejos 12V 3A

$ 58.00 - $ 65.00Rango de precios: desde $ 58.00 hasta $ 65.00

GX-9877 Interruptor Tactil Unicolor/Bicolor para Espejos 12V 3A

$ 58.00 - $ 65.00Rango de precios: desde $ 58.00 hasta $ 65.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Boton Tactil Capacitivo Verde/Rojo/Azul

$ 26.00

Boton Tactil Capacitivo Verde/Rojo/Azul

$ 26.00 -

Add

RG6-305 Cable Coaxial 1m 75 Ohms C/50% Malla

$ 6.00

RG6-305 Cable Coaxial 1m 75 Ohms C/50% Malla

$ 6.00

Subtotal: $ 2,724.00

Valoraciones

No hay valoraciones aún.