-

×

FC-37 Sensor de Lluvia para Arduino

1 × $ 27.00

FC-37 Sensor de Lluvia para Arduino

1 × $ 27.00 -

×

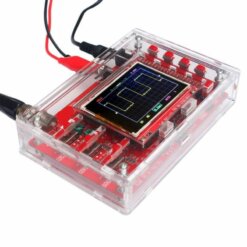

Osciloscopio DSO138 con Carcasa y Display TFT

1 × $ 452.00

Osciloscopio DSO138 con Carcasa y Display TFT

1 × $ 452.00 -

×

Kit Makey Makey DIY USB Tipo C

1 × $ 422.00

Kit Makey Makey DIY USB Tipo C

1 × $ 422.00 -

×

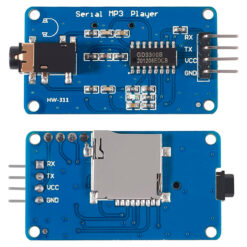

ARYX5300 Reproductor MP3 WAV UART Micro SD

1 × $ 79.00

ARYX5300 Reproductor MP3 WAV UART Micro SD

1 × $ 79.00 -

×

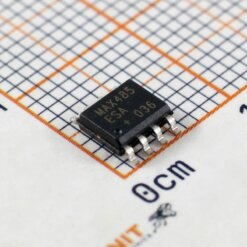

MAX485ESA+T IC SMD Transceptor

1 × $ 24.00

MAX485ESA+T IC SMD Transceptor

1 × $ 24.00 -

×

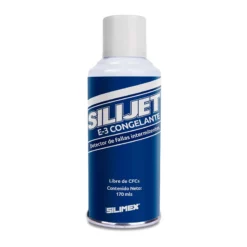

Congelante Detector de Falla para Circuitos Electrónicos 170 ml SILIJET E-3

1 × $ 109.00

Congelante Detector de Falla para Circuitos Electrónicos 170 ml SILIJET E-3

1 × $ 109.00 -

×

PZEM-031 Voltimetro Digital LCD 100V 20A

1 × $ 286.00

PZEM-031 Voltimetro Digital LCD 100V 20A

1 × $ 286.00 -

×

Conector de Audio XLR 3 Pines Plateado Hembra y Macho

1 × $ 47.00

Conector de Audio XLR 3 Pines Plateado Hembra y Macho

1 × $ 47.00 -

×

Estación de Soldadura con Brazos Flexibles

1 × $ 728.00

Estación de Soldadura con Brazos Flexibles

1 × $ 728.00 -

×

Kit Terminales Termorretráctiles 250pcs SV, MDD, RV, BHT y FDFD

1 × $ 328.00

Kit Terminales Termorretráctiles 250pcs SV, MDD, RV, BHT y FDFD

1 × $ 328.00 -

×

Tarjeta MicroSD de 64GB Preprogramada con Raspbian para Raspberry Pi

1 × $ 329.00

Tarjeta MicroSD de 64GB Preprogramada con Raspbian para Raspberry Pi

1 × $ 329.00 -

×

Cable para Batería de 9V con Broche

1 × $ 8.00

Cable para Batería de 9V con Broche

1 × $ 8.00 -

×

DP-366D Desoldador de Succión

1 × $ 49.00

DP-366D Desoldador de Succión

1 × $ 49.00 -

×

Kit Conectores LT41 de Empalme Rápido 75pcs

1 × $ 208.00

Kit Conectores LT41 de Empalme Rápido 75pcs

1 × $ 208.00

Puede que estés interesado en…

-

Add

Pasta Limpiadora para Puntas de Cautín 6g

$ 34.00

Pasta Limpiadora para Puntas de Cautín 6g

$ 34.00 -

Add

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

$ 159.00

CAU-115A Cautin Tipo Lapiz de 35W 127V con Accesorios

$ 159.00 -

Add

HB-019 Desoldador de Succión Eléctrico 36W 110V

$ 139.00

HB-019 Desoldador de Succión Eléctrico 36W 110V

$ 139.00 -

Add

Toallitas Húmedas para Limpieza de Equipos Electrónicos 30pcs COMPUTOALLAS

$ 59.00

Toallitas Húmedas para Limpieza de Equipos Electrónicos 30pcs COMPUTOALLAS

$ 59.00 -

Add

Limpiador Dieléctrico para Circuitos y Tarjetas Electrónicas 454 ml COMPUKLIN

$ 189.00

Limpiador Dieléctrico para Circuitos y Tarjetas Electrónicas 454 ml COMPUKLIN

$ 189.00

Subtotal: $ 3,096.00

Valoraciones

No hay valoraciones aún.