-

×

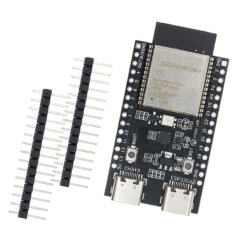

ESP32-C6 DevKit Dual Tipo C NanoESP32-C6 V1

1 × $ 187.00

ESP32-C6 DevKit Dual Tipo C NanoESP32-C6 V1

1 × $ 187.00 -

×

WEAH-T-5 Tweeter Crossover 40W Tipo A 2.2UF

1 × $ 60.00

WEAH-T-5 Tweeter Crossover 40W Tipo A 2.2UF

1 × $ 60.00 -

×

TE-808 Lupa de Soldadura con Abrazadera Universal

1 × $ 635.00

TE-808 Lupa de Soldadura con Abrazadera Universal

1 × $ 635.00 -

×

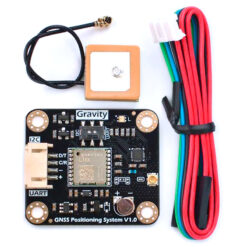

TEL0157 Receptor BeiDou GNSS GPS I2C y UART

1 × $ 410.00

TEL0157 Receptor BeiDou GNSS GPS I2C y UART

1 × $ 410.00 -

×

Paquete De 4 Pilas Alcalinas AA

1 × $ 59.00

Paquete De 4 Pilas Alcalinas AA

1 × $ 59.00 -

×

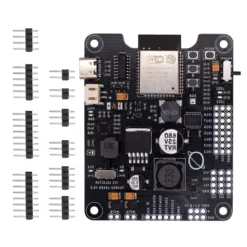

Tuxedo 18650 Rocket Launcher

1 × $ 589.00

Tuxedo 18650 Rocket Launcher

1 × $ 589.00 -

×

Sensor TDS Meter V1.0 Analógico

1 × $ 281.00

Sensor TDS Meter V1.0 Analógico

1 × $ 281.00 -

×

Fuente de Alimentación Universal 3V-24V 2A 48W

1 × $ 176.00

Fuente de Alimentación Universal 3V-24V 2A 48W

1 × $ 176.00 -

×

WT32-SC01 ESP32 Pantalla Táctil 3.5" 320X480

1 × $ 849.00

WT32-SC01 ESP32 Pantalla Táctil 3.5" 320X480

1 × $ 849.00 -

×

TEMT600 Sensor de Luz Ambiental – UNIT DevLab

1 × $ 39.00

TEMT600 Sensor de Luz Ambiental – UNIT DevLab

1 × $ 39.00 -

×

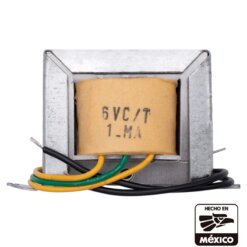

Transformador 6VC/T 1A con Tap Central

1 × $ 153.00

Transformador 6VC/T 1A con Tap Central

1 × $ 153.00

Puede que estés interesado en…

-

Add

Sensor de Gestos y Detección de Rostros con AI SEN0626

$ 445.00

Sensor de Gestos y Detección de Rostros con AI SEN0626

$ 445.00 -

Add

UNIT Pulsar ESP32-C6

$ 189.00

UNIT Pulsar ESP32-C6

$ 189.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

Sensor de Estación Meteorológica con Caja de Rejilla

$ 558.00 - $ 1,309.00Rango de precios: desde $ 558.00 hasta $ 1,309.00

Sensor de Estación Meteorológica con Caja de Rejilla

$ 558.00 - $ 1,309.00Rango de precios: desde $ 558.00 hasta $ 1,309.00 -

Add

Sensor de Luz UV 290-390nm (UVA, UVB) RS485 SEN0642

$ 1,376.00

Sensor de Luz UV 290-390nm (UVA, UVB) RS485 SEN0642

$ 1,376.00 -

Add

Este producto tiene múltiples variantes. Las opciones se pueden elegir en la página de producto

GA12-N20 Motorreductor DC 3V / 6V / 12V

$ 80.00 - $ 97.00Rango de precios: desde $ 80.00 hasta $ 97.00

GA12-N20 Motorreductor DC 3V / 6V / 12V

$ 80.00 - $ 97.00Rango de precios: desde $ 80.00 hasta $ 97.00

Subtotal: $ 3,438.00

Valoraciones

No hay valoraciones aún.